This article was downloaded by: [Mohd Khairuddin Md Arshad] On: 21 February 2015, At: 06:41 Publisher: Taylor & Francis Informa Ltd Registered in England and Wales Registered Number: 1072954 Registered office: Mortimer House, 37-41 Mortimer Street, London W1T 3JH, UK

# Critical Reviews in Solid State and Materials Sciences

Publication details, including instructions for authors and subscription information: <u>http://www.tandfonline.com/loi/bsms20</u>

# Fully Depletion of Advanced Silicon on Insulator MOSFETs

M.K. Md Arshad<sup>a</sup>, N. Othman<sup>a</sup> & U. Hashim<sup>a</sup>

<sup>a</sup> Institute of Nano Electronic Engineering, Universiti Malaysia Perlis, Kangar, Perlis, Malaysia Published online: 18 Feb 2015.

To cite this article: M.K. Md Arshad, N. Othman & U. Hashim (2015): Fully Depletion of Advanced Silicon on Insulator MOSFETs, Critical Reviews in Solid State and Materials Sciences, DOI: <u>10.1080/10408436.2014.978447</u>

To link to this article: <u>http://dx.doi.org/10.1080/10408436.2014.978447</u>

### PLEASE SCROLL DOWN FOR ARTICLE

Taylor & Francis makes every effort to ensure the accuracy of all the information (the "Content") contained in the publications on our platform. However, Taylor & Francis, our agents, and our licensors make no representations or warranties whatsoever as to the accuracy, completeness, or suitability for any purpose of the Content. Any opinions and views expressed in this publication are the opinions and views of the authors, and are not the views of or endorsed by Taylor & Francis. The accuracy of the Content should not be relied upon and should be independently verified with primary sources of information. Taylor and Francis shall not be liable for any losses, actions, claims, proceedings, demands, costs, expenses, damages, and other liabilities whatsoever or howsoever caused arising directly or indirectly in connection with, in relation to or arising out of the use of the Content.

This article may be used for research, teaching, and private study purposes. Any substantial or systematic reproduction, redistribution, reselling, loan, sub-licensing, systematic supply, or distribution in any form to anyone is expressly forbidden. Terms & Conditions of access and use can be found at <a href="http://www.tandfonline.com/page/terms-and-conditions">http://www.tandfonline.com/page/terms-and-conditions</a>

## **Fully Depletion of Advanced Silicon on Insulator MOSFETs**

## M.K. Md Arshad<sup>\*</sup>, N. Othman, and U. Hashim

Institute of Nano Electronic Engineering, Universiti Malaysia Perlis, Kangar, Perlis, Malaysia

Scaling of the transistor has been tremendous successful in the beginning with reduction of the gate oxide thickness and increase of doping concentration. Moving into smaller dimension, those are not enough to overcome the short channel effect. Starting with changing in materials and followed by device architecture is needed which require fully depletion operation. This article reviews the fully-depletion operation of thin body of silicon on insulator of advanced MOSFETs.

Keywords: fully-depletion, SOI MOSFETs, thin-body and thin-buried oxide (UTBB)

#### **Table of Contents**

| 1.  | INTRODUCTION                             | . 1 |

|-----|------------------------------------------|-----|

|     |                                          |     |

| 2.  | SILICON ON INSULATOR (SOI)               | . 3 |

|     | 2.1. PD and FD-SOI MOSFETs.              | . 3 |

|     | 2.2. Short Channel Effects in SOI        | . 5 |

| 3.  | FD-SOI MOSFETs                           | . 5 |

|     | 3.1. MASTAR Equations                    | . 5 |

|     | <ul> <li>3.1. MASTAR Equations</li></ul> | . 7 |

|     | 3.3. Figures-of-Merit                    | . 8 |

| 4.  | CONCLUSION                               | . 9 |

| REI | FERENCES                                 | 10  |

|     |                                          |     |

#### 1. INTRODUCTION

In 1965, Gordon Moore, a co-founder of both Fairchild and Intel, described in his paper, based on five data points available from Fairchild at that time: "with unit cost falling as the number of components per circuit rises, by 1975 economics may dictate squeezing as many as 65,000 components on a single silicon chip.".<sup>1</sup> Ten years later, in 1975, he revisited the prediction and surprisingly the actual data scatter pretty well along the prediction line, which evidenced that the number of devices per integrated circuit increase exponentially with increasing time. This astonishing prediction was later famously named as Moore's Law and has brought significant impact to the industry. Moreover, it later became a basis of industry forecasts such as those of the ITRS<sup>2</sup> for transistor scaling.

The successful of this classical scaling is initially supported with the scaling concept published by Dennard in 1974,<sup>3</sup> as illustrated in Table 1 (constant-field scaling). The simple concept of scaling is to reduce all of the physical dimensions by the same amount of  $\alpha$ . To keep the electric field constant, the channel doping needs to be increased and the applied voltage to be reduced. This will cause the depletion regions within the devices to scale as much as the other dimensions. A first important result of scaling is increased circuit density since the area is divided by  $\alpha^2$ . This was seen as a key to reducing

<sup>\*</sup>E-mail: mohd.khairuddin@unimap.edu.my

Color versions of one or more of the figures in the article can be found online at www.tandfonline.com/bsms.

TABLE 1 Scaling factors ( $\alpha$ ) for the classical scaling trends

| Parameter                                       | Constant-<br>field<br>scaling <sup>3</sup> | Generalized<br>scaling<br>factor <sup>4</sup> |

|-------------------------------------------------|--------------------------------------------|-----------------------------------------------|

| Physical dimensions (L, W, $T_{ox}$ , $X_{j}$ ) | 1/α                                        | 1/α                                           |

| Electric field $(\in)$                          | 1                                          | E                                             |

| Body doping concentration (N <sub>a</sub> )     | α                                          | $\in /\alpha$                                 |

| Supply voltage (V <sub>dd</sub> )               | $1/\alpha$                                 | $\in /\alpha$                                 |

| Transistor current (I)                          | $1/\alpha$                                 | $\in /\alpha$                                 |

| Capacitance (C = $\varepsilon_{ox}A/T_{ox}$ )   | $1/\alpha$                                 | $1/\alpha$                                    |

| Area (A)                                        | $1/\alpha^2$                               | $1/\alpha^2$                                  |

| Gate delay ( $\tau \sim CV_{dd}/I$ )            | 1/α                                        | $\in /\alpha$                                 |

| Power dissipation ( $P \sim IV_{dd}$ )          | $1/\alpha^2$                               | $\in^2/\alpha^2$                              |

| Power density (P/A)                             | 1                                          | $\in^{2}$                                     |

manufacturing costs. A second important result that underlies the speed and power benefits by a factor of  $\alpha$  and  $\alpha^2$ , respectively, is the reduction of capacitance per circuit. Furthermore, as a constraint of the voltage that is not usually scaled as fast as the linear dimension due to subthreshold leakage constraint, additional scaling factor  $\in$  for the electric field is introduced to account for the increased of electric field ( $\in$  is greater than one). This is summarized under "generalized scaling factor."<sup>4</sup>

The continuous and systematic increase in transistor density and performance, as described in Moore's Law and guided by Dennard's scaling theory, has been remarkably successful for the development of silicon MOSFET technology for the past 50 years. This can be seen with many generations of smaller devices and significant increase of transistors count per chip for faster, power efficient and high performance microprocessors and more importantly at reduced cost. This classical MOSFET scaling technique was followed successfully until 90 nm transistor generation<sup>5-8</sup> (130 nm was the last CMOS generation where making the transistor smaller was sufficient to deliver performance improvement). In the subsequent generation, classical scaling technique is insufficient to increase the performance, but in turn, it might degrade the performance. For example, scaling down the gate oxide leads to an increase of gate leakage current which severely degrades the transistor performance. When gate oxide can no longer be scaled, the other key MOSFET parameters such as supply voltage can no longer be scaled and yet the transistor is still expecting to deliver improvement in performance. Without new invention and progressive research MOSFET scaling and Moore's Law were jeopardized likely near to their end.

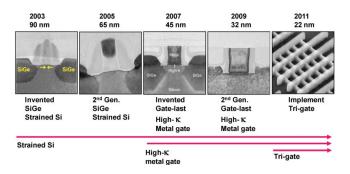

In 2003, one of the first significant transistor innovations was the introduction of strained-silicon technology to enhance transistor performance in 90 nm technology.<sup>9–11</sup> In PMOS, SiGe was selectively deposited on source-drain regions to provide compressive channel strain that improves holes mobility while in NMOS a tensile SiN cap layer was deposited over

the transistors to provide tensile channel strain to improve electrons mobility. The 65 nm generation introduced two years later further improved these strain techniques and subsequently increase the transistor performances.<sup>12,13</sup> In these two technology nodes, the gate-oxide thickness was roughly un-scaled to remain approximately 1.2 nm,<sup>9,12</sup> which is about five atomic layers of Si oxide. The strained-silicon was considered revolutionary technology since it provides satisfactory performance enhancement for 90 and 65 nm generations when the classical MOSFET scaling methods are no longer effective.

Nevertheless, there was a need to reduce the gate-oxide leakage with high- $\kappa$  technology for reduced leakage and improved performances. A hafnium-based dielectric (high- $\kappa$ material) was introduced in 45 nm<sup>14,15</sup> generation node as replacement to SiO<sub>2</sub>. High- $\kappa$  material provides a gate oxide that is physically thicker, which reduces leakage, but has thinner electrical equivalence, which improves transistor performance. The polysilicon gate electrode was replaced by two different metal-gate materials (for NMOS and PMOS) to eliminate the poly-depletion effect. The thin gate oxide provided by high- $\kappa$  and the metal gate also helped to reduce transistor V<sub>Th</sub> variability.<sup>16</sup> In addition, the 45 nm generation introduces different process flow known as gate-last. The gate-last flow allows the metal gate materials to be deposited after high temperature source and drain formation steps are completed, thus offering a wider set of materials options for tuning NMOS and PMOS gate-work functions. As a result, the gate-last flow has additional benefit of enhancing channel strain during the removal of the sacrificial polysilicon gate<sup>15</sup> which further increase the transistor performances.

The 32 nm technology node utilized second generation of high- $\kappa$  and metal-gate transistors along with previous benefits obtained in fourth generation of strained silicon.<sup>17,18</sup>

For the latest 22 nm generation node, Trigate 3D-MOSFET architecture has been opted to extend the scalability with improvement in performances compared to classical planar transistor.<sup>19</sup> Trigate provides fully depleted operation due to narrow fins, as the fins are wrapped by the gate electrode around three sides, providing improved electrostatic control of the channel. The improved channel control provides steep sub-threshold slope, reduced leakage current, higher performances, etc. Although there is a significant improvement in term of electrostatic behavior, but this alone is not sufficient to deliver the expected performance and benefits. The strained Si, gate-last process, and high- $\kappa$  and metal gate still need to be applied as in previous nodes.

Figure 1. depicts the chronological advancement in materials and structures for 90 nm down to 22 nm technology nodes as previously discussed.

Now, one can see that, as the transistor moves into extreme smaller dimensions, it needs to incorporate innovations such as strained-Si, high- $\kappa$  + metal gate, and 3D-structures. It is no longer limited to shrinking the geometries to make more space available for more transistors at reduced cost per transistor,

FIG. 1. Evolution of transistor in each technology nodes for continuous improvement of performances.<sup>19</sup>

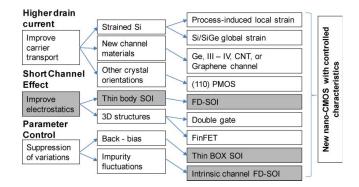

but it involves materials advancement, new structures as well advances in processes which need to be integrated together for achieving the same goals. In the next generation, continuing the shrinking is even more challenging. In response to that, several approaches have been identified with some of them addressed and implemented while some are still at the research levels. Figure 2 illustrates the possible solutions:<sup>20,21</sup>

- Improve the carrier transport properties by introducing new materials. The strained-Si technology has been widely used to achieve high drive currents. As shown in Figure 2, silicon only as a channel is not necessarily the best material anymore. Changing the channel material or incorporating silicon channel with higher mobility materials (SiGe, Ge, III-V semiconductors, or carbon nanotubes) will lead to further performance improvement to extend the CMOS generation.

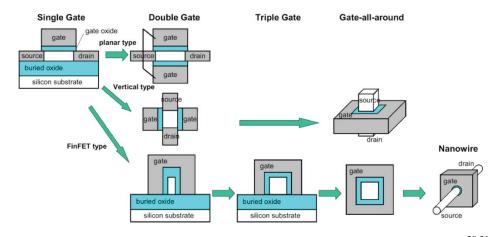

- Improve the electrostatics of MOSFETs by introducing new structures. Different transistor structures (Figure 3) should be considered to improve the electrostatics and control of short-channel effect especially when entering sub-nanometer regime. A double-gate transistor has much better short channel effect immunity than a single-gate transistor because of better control of the channel by the gates. The ideal device structure in terms of the electrostatic control is

FIG. 2. Major challenges and possible technical solutions for extending CMOS scalability.<sup>20,21</sup>

a gate-all-around which leads to the nanowire transistor structure.

• *Suppress the variability.* In order to thoroughly eliminate Random Dopant Fluctuation (RDF) problem, a transistor with an intrinsic channel is required, which can be achieved in fully-depleted silicon-on-insulator (FD-SOI) structure.

The next generation of transistors should be able to solve all the challenges mentioned, with combinations of solutions preferable to achieve the improvement in performances. Of course to discuss everything is single article will be very lengthy, thus we focus on the thin body silicon-on-insulator.

#### 2. SILICON ON INSULATOR (SOI)

SOI technology provides a good insulation from substrate injection noise (crosstalk) due to the oxide insulation between devices especially between the analog and digital devices. It provides an additional degree of freedom when selecting the resistivity of the substrate to reduce the capacitive coupling and the losses.<sup>22–24</sup> In addition, the shallow junction is easy to achieve (in the case of thin silicon film) thanks to its dependence on silicon thickness.

SOI also features some drawbacks such as self-heating. In SOI devices the heat dissipation is not as efficient as in bulk Si due to presence of the insulator which has lower thermal conductivity than silicon. This can lead to performance device degradation or sometime failure over the operating period. However, self-heating is expected to be improved with implementation of thin BOX.<sup>25–27</sup>

For the case with thicker silicon film, partially depleted devices are more prone to undesirable results due to floatingbody effects. For fully depleted SOI (thinner Si film), one needs stringent manufacturability process control on the uniformity of the silicon thickness and to prevent the surface states at the BOX/substrate interface. Similarly if the thin BOX is employed, the quality of thin BOX and the interface requires stringent control.<sup>28,29</sup>

#### 2.1. PD and FD-SOI MOSFETs

In classical SOI transistor, the current flows between source and drain are controlled primarily by the gate and secondarily by the substrate bias that acts a back gate. As a result, two inversion channels may be activated, i.e., at the front Si-SiO<sub>2</sub> interface (front interface) and at the Si-BOX interface (back interface). In PD-SOI the two space-charge regions are independent and for FD they are coupled. This behavior is very much related to the thickness and doping of the silicon films and can be categorized physically depending on the maximum depletion width ( $X_{dmax}$ ) given by (1):

$$X_{dmax} = \sqrt{\frac{4\varepsilon_{Si}\Phi_F}{qN_A}}$$

(1)

FIG. 3. Transistor evolution from single-gate and double-gate to nanowire transistor.<sup>20,21</sup>

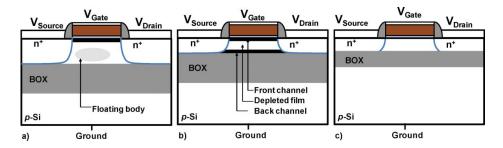

Partially depleted SOI (Figure 4a) can be defined as device for which the silicon film is larger than twice the value of  $X_{dmax}$ .<sup>22</sup> This commonly occurs in thick film SOI devices or depending on doping concentration in the Si films. The silicon and buried oxide thickness of 50–90 nm and 50–145 nm, respectively, can be considered as PD-SOI devices.<sup>30</sup> PD-SOI features similar characteristics as in bulk as the body is never completely depleted. Two independent channels may be formed close to the interfaces, with presence of a neutral region in between. This neutral region is known as a floating body effect (FBE) which leads to undesirable device performance such as kink-effect, parasitic BJT effects, anomalous subthreshold slope, reduced drain breakdown voltage, and other effects. The problems are diminished in body-tied or dynamic-threshold MOSFET (DTMOS) structures.<sup>23,28,31</sup>

Fully depleted (Figures 4b,c) SOI can be obtained when the silicon film thickness is smaller than  $X_{dmax}$ .<sup>22</sup> Ultra-thin silicon with standard buried oxide (UTB; Figure 4b) and ultra-thin silicon with ultra-thin buried oxide (UTBB; Figure 4c) can be considered as fully-depleted devices. As a guide, silicon and BOX thicknesses of less than 30 nm and 150 nm is considered as UTB, while for UTBB, the BOX is much thinner, notably below 50 nm.<sup>30</sup>

In FD-SOI, the depletion region covers the whole transistor body irrespective of the bias applied to the back gate. As a result, the front- and back-channel are coupled, therefore the electrical characteristics of one channel depends on the bias applied to the opposite gate. This excellent coupling offers improved drive current and near ideal subthreshold slope<sup>22,23,31-33</sup> due to smaller body factor. Body factor (normally represented by the letter n), is an image of the coupling efficiency between the front-gate voltage and the channel. The closer *n* is to unity, the sharper the transition between the off and on-states of the transistor. More detailed explanation about the body factor can be found here. Since the body film is fully depleted, the device characteristics become more complex, i.e., the front-gate characteristics include contributions from the BOX/Si interface and highly depend on the back-gate bias. The FD-SOI devices can be considered free from FBE effects. For FD-SOI with ultra-thin body (typically  $\sim < 10$  nm), due to super-coupling effect<sup>34</sup> accumulation regime at the back interface cannot be achieved with simultaneous inversion at front interfaces or visa-versa. In this case, the potential distribution remains constant along the front- to the back-gate of the channel. Super-coupling effect is not only dependent on silicon body thickness, but also ultra-thin BOX with combination of applied voltage between the front and back-gates.

The above definitions can be used to distinguish between PD and FD-SOI, typically for thick and thin Si body, respectively. However, there is a region with medium thickness of

FIG. 4. Basic architecture of (a) partially depleted (PD), (b) ultra-thin body with standard buried oxide thickness (UTB) FD,<sup>23</sup> and (c) ultra-thin body and ultra-thin buried oxide (UTBB) FD-SOI MOSFETs.

SOI body where  $X_{dmax} < t_{Si} < 2.X_{dmax}^{22}$  which can be said as transition between partial to full depletion. In this case, the device operation can be changed from PD to FD due to contribution of source and drain lateral depletion regions. It is dependent on gate length, channel doping and back-gate bias.<sup>22,29,35</sup> This criterion is only valid for classical SOI MOS-FETs and it does not occur for advanced SOI MOSFETs featuring thin Si body and thin buried oxide.

#### 2.2. Short Channel Effects in SOI

Short channel effects (SCE) are the phenomena by which the threshold voltages are seen to decrease and off-state current seen to increase as the gate length is reduced. This is a consequence of the fact that as gate length is decreased, the depletion regions associated with the source and drain regions become closer and start to interact with each other. These depletion regions are the region of high electric fields which propagate through the depletion regions associated with the junctions. They facilitate carrier transport directly between the source and drain regions, which gives rise to the observed phenomena of higher off-state currents, reduced threshold voltages and reduced control of the gate over the channel, thus degraded transistor characteristics.

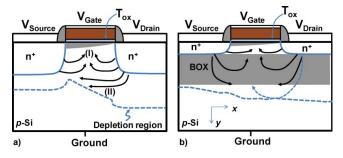

Figure 5a illustrates the electric field lines in bulk Si devices. Classical bulk Si scaling approaches have dealt with this problem by requiring an increase of body doping (region I and II in Figure 5a), thereby decreasing the depletion widths and electric field propagations associated with the source and drain, so that these two junctions are kept separated to the larger extent possible. However, increasing the body doping is accompanied by severe drawbacks such as degraded mobility, increased capacitances, and increased statistical fluctuations, all of which pose serious challenges to scaling. Other scaling challenges include those such as high gate currents, high parasitic resistances and capacitances, large interconnect delays, etc.

Figure 5b illustrates the electric field in SOI MOSFETs device. In SOI, most of the electric field propagates through the BOX before reaching the channel region. Short channel effects in SOI devices can be controlled in different way as

FIG. 5. Illustration of electric field encroachment, emanating from the source and drain toward the channel region (a) bulk Si and (b) FD-SOI MOSFETs.

derived from (2):<sup>36,37</sup>

$$\lambda = \sqrt{\frac{\varepsilon_{\rm Si}}{\varepsilon_{\rm ox}}} {\rm T}_{\rm Si} {\rm T}_{\rm ox}}, \qquad (2)$$

where  $\lambda$  is the natural length which represents the spread of the electric potential in the x-direction along the source and drain. It shows dependence on the gate oxide and silicon oxide thicknesses. The thinner the gate oxide and/or the silicon film, the smaller the natural length, and hence it allows to reduce the influence of the lateral electric field in the channel region. Unlike the approach used in bulk Si to reduce SCE, the increase of channel doping in SOI devices is less efficient compared with reducing the natural length directly.<sup>36</sup> Incorporate SOI devices with ground plane and thin buried oxide allows further improvement since most of the electric fields from the source and drain terminate on the ground plane instead of channel region.

#### 3. FD-SOI MOSFETs

#### 3.1. MASTAR Equations

MASTAR stands for Model for Assessment of CMOS Technologies And Roadmaps.<sup>38</sup> MASTAR equations are derived based on empirical data and have been established and confirmed throughout a number of past CMOS generations.<sup>39–42</sup> Moreover, this model has been implemented in the predicting tools used by ITRS<sup>2</sup> for Process Integration, Devices, and Structures report to calculate the impact of transistor scaling on electrical characteristics.

For bulk,

$$EI = \left(1 + \frac{X_j^2}{L_{el}^2}\right) \left(\frac{T_{oxel}}{L_{el}} \cdot \frac{T_{dep}}{L_{el}}\right)$$

(3)

$$EIS = \left(\frac{T_{oxel}}{L_{el}} \cdot \frac{X_j}{L_{el}}\right) \left(1 + \frac{3}{4} \cdot \frac{T_{dep}}{L_{el}}\right)$$

(4)

$$SCE = 0.64 \left( \frac{T_{Si}}{T_{ox}} \right) . EI. \Phi_d$$

(5)

$$\text{DIBL} = 0.80 \frac{\varepsilon_{\text{Si}}}{\varepsilon_{\text{ox}}} (\text{EI}) \text{V}_{\text{ds}}$$

(6)

$$S = \frac{kT}{q} . \ln(10) . \left[ 1 + \frac{C_{dep}}{C_{ox}} + \frac{T_{si}}{T_{ox}} EIS \sqrt{1 + 2\frac{V_{ds}}{\Phi_d}} \right], \quad (7)$$

where  $X_j$  is junction depth,  $L_{el}$  is electrical gate length,  $T_{oxel}$  is electrical oxide thickness,  $T_{dep}$  is depletion thickness,  $T_{si}$  is silicon thickness,  $T_{ox}$  is oxide thickness, is drain potential,  $C_{dep}$  is depletion capacitance, and  $C_{ox}$  is oxide capacitance.

Electrostatic Integrity (EI) in (3) has relation to SCE and DIBL, while EIS (Electrostatic Integrity specifically for subthreshold slope) in (4) is related to subthreshold slope. EI and EIS equations will be used to explain the behaviors of FD-SOI

devices as the gate length is scaled and for better understanding, the comparison is made with planar bulk Si devices.

The ratios of  $T_{oxel}/L_{el}$ ,  $X_j/L_{el}$ , and  $T_{dep}/L_{el}$  that appear in EI and EIS are called "good technology rules" and these parameters are depicted in Figure 5. For (a) bulk Si and (b) SOI MOS-FETs. These rules describe the quality of the transistor in the subthreshold regime by ensuring good electrostatic integrity of the device. In other words, keeping these ratios constant from one generation to another preserves the value of SCE, DIBL and S throughout the scaling devices. Typically, the three ratios used to reach 1/27, 1/2, and 1/2, respectively.<sup>39</sup>

In the first parameter, to avoid high off-state current and poly-depletion effect, the scaling of  $T_{oxel}/L_{el}$  ratio needs to be sustained. With scaling of SiO<sub>2</sub> approaching the limit, high- $\kappa$ materials are required. For bulk CMOS, high- $\kappa$  materials cointegration with dual metal schemes significantly increase the process complexity compared to a poly-silicon-gate technology.<sup>39</sup> The big advantage of polysilicon gates is the modulation of its work function by implantation. This property is not obtainable with metallic gates. Implementation of single-gate (mid-gate function, e.g., TiN and W) metals is inadequate for advanced bulk silicon as follows.<sup>42,43</sup>

- Resulting threshold voltages are too large for lowvoltage operation. They are increased or decreased by half of the silicon gap for NMOS and PMOS, respectively.

- Short channel characteristics are severely degraded due to low substrate doping density.

However, there are several approaches to overcome the problem with co-integration of dual metallic gates into the CMOS gate stack,<sup>39,44</sup> i.e., traditional etching,<sup>42</sup> Total Silicidation (TOSI) or Fully Silicidation (FUSI),<sup>42,43</sup> and gate-last damascene,<sup>42,43</sup> with the later method being most preferable.<sup>44</sup> While in FD-SOI ultra-thin body devices, the implementation of a single gate (mid-gap) is straightforward<sup>39,42,45,46</sup> since the difference between NMOS and PMOS gate work function is relatively small for undoped channel. Undoped channel is the channel that does not require additional intrinsic carriers, i.e., the channel doping can be kept to low about ~  $10^{15}$  cm<sup>-3</sup>, which is impossible for bulk Si due to SCE. In addition, UTB offers lower threshold voltage than their bulk counterparts thanks to negligible depletion charge in the channel, without increasing the off current.<sup>39</sup>

The second parameter which controls the scaling of the device is a reduction in junction depth following the reduction of gate length, i.e.,  $X_j/L_{el.}$  This term faces difficulties in bulk Si due to uncertain technological feasibility,<sup>47</sup> but also the trade-off between depth and resistivity is an issue. If the junction depth is shallow and smaller than the inversion layer, the source, drain, and channel regions will be partially disconnected, or the resistance between the regions will be very high, resulting in large degradation of

the drive current.<sup>3,48</sup> Another foreseen issue is that it requires tight control of manufacturability in terms of narrow doping profiles. Therefore, UTB can offer great advantage with respect to the shallow-junction problem since the junction depth is then limited to the thickness of the channel. Thanks to that, the depth of the junction is also decoupled from its doping level, thus diminishing the junction resistivity problem.<sup>39,40</sup>

The third parameter is the depletion depth ( $T_{dep}$ ), similar to junction depth; the depletion depth can also be limited by geometry in UTB devices. In bulk devices, the limitation in the channel hinders the  $T_{dep}$  scaling (regions I and II). Several limitations prevent high channel doping i.e. significant junction leakage, increased statistical fluctuation due to random dopant fluctuation in the channel, strong degradation in mobility due to impurity scattering and an increased transverse electric field. In extreme case, the mobility degradation may dominate the beneficial effect of channel shortening. This eventually leads to a current decrease instead of increase in shorter devices.<sup>36,39,41,42,49</sup> In UTB devices, the effective depletion depth is geometrically limited to the silicon, BOX thickness, and sometimes small effect of substrate depletion depth ( $T_{Sub}$ ).

Based on those merits, one can see that UTB FD-SOI is superior with respect to EI. The main key is that, both the X<sub>i</sub> and T<sub>dep</sub> are no longer results of doping and diffusion. Instead, they are set by the thickness of the silicon film and therefore, can be much smaller than  $X_i$  and  $T_{dep}$ in bulk devices. Moreover, based on those explanations, UTB devices have potential to extend MOSFET scalability. However, when discussing about scalability of FD-SOI with thin body, it is more appropriate to include thin buried oxide as well (UTBB). This is due to the fact that only thinning silicon body is not sufficient for very good scalability of SOI MOSFETs but also the thickness of underlying BOX. This can be explained with significant reduction of electrostatic field penetration, emanating laterally from the drain into the BOX towards the source and channel inversion<sup>39,50-52</sup> and thus degrading the subthreshold characteristics. For that reason, when hypothesizing about scalability in FD-SOI MOSFETs, it is more appropriate to focus on UTBB devices. However, thin BOX triggers stronger coupling between the gate and substrate, and if substrate is lightly doped (particularly underneath the BOX/substrate interface), it will be depleted by the gate and drain fields. This depleted layer will then behave as dielectric and effectively add to the physical thickness of the BOX<sup>53</sup> and thus loses it advantages. Ground plane implementation can be used to suppress this unwanted effect.

As a final point, one can see, for scalability of UTB and UTBB SOI MOSFETs, the terms  $X_j$  and  $T_{dep}$  in (3) and (4) can be replaced with  $T_{Si}$  and  $T_{Si} + \gamma T_{BOX}$ ,<sup>38,39</sup> respectively with  $\gamma$  to take into account the substrate depletion depth.

#### 3.2. UTBB Electrostatic Features

As previously discussed, the scaling principles of bulk silicon MOSFETs device require a reduction of junction depth and an increase of doping level, which adversely affect the junction capacitance and carrier mobility. Similar difficulty arises for PD-SOI with regards to channel and junction doping since PD-SOI characteristics are almost similar to bulk silicon (due to thicker silicon body). Fortunately, FD-SOI has emerged as promising technology as those two bottleneck parameters are diminished in FD-SOI. In addition, the scaling rules and design windows are more relaxed because additional tunable parameters (BOX thickness, channel free from doping, underlap channel, substrate doping, and backgate biasing) are available for device optimization. In this section, we will look into the electrostatic integrity features of FD-SOI MOSFETs (particularly UTBB) to extend the scalability of CMOS and to continue enjoying increased performances.

First, the basic concept of using ultra-thin silicon body is to reduce the SCE as explained by natural length expression ((2)) and MASTAR equation. Second, by reducing the silicon body thickness, the leakage current which flows along the bottom between source and drain, which is less effectively controlled by the front gate, can be reduced.<sup>49,54–56</sup> This allows the channel to be undoped. With undoped channel, higher carrier mobility can be reached that further improves the drive current, thanks to lower transverse electrostatic field and negligible impurity scattering. It also features negligible depletion charge and low junction capacitances which yield steep sub-threshold slope.<sup>49</sup> Moreover, significantly improved variability control can be achieved due to elimination of random dopant fluctuation.<sup>51,57–62</sup>

However, thin silicon body induces high parasitic source and drain resistances. There are several approaches reported in the literature to overcome this effect. One is to use thicker raised source and drain (RSD) to minimize the parasitic series resistances and achieve high drain current.<sup>49,51</sup> However, there is a trade-off with this approach as one can gain benefit from minimizing the effect of parasitic resistances but degrade the circuit performances due to increased parasitic capacitances between the gate and source and drain electrodes, i.e., fringing capacitances. Therefore, in this approach the spacer width between gate and RSD should be optimized. The second approach to reduce the parasitic resistances is to use metallic or silicided source and drain,<sup>51,54,55</sup> with very low Schottkybarrier in order to not degrade the drive current. A last method is known as faceted raised source and drain (faceted RSD). The faceted RSD do not only reduce the series resistance but also minimize the parasitic capacitances.<sup>63–66</sup> The method has been implemented in SRAM cell with reduction delay time, thus affirming the benefit of capacitance reduction.<sup>67</sup>

Second, in FD-SOI, the channel can be kept undoped due to above reason, such that the implementation of underlap is more feasible in FD-SOI<sup>68</sup> compared to bulk.<sup>69</sup> With underlap,

the effective channel length increases thus decreasing the drive current due to an increase of series source and drain resistances. Moreover, the off-state current is reduced due to the suppression of DIBL and subthreshold slope is improved. Hence, there is a trade-off between improved short channel behavior and reduced drive current in devices with longer extension lengths.<sup>68,70,71</sup> Nevertheless, underlap is reported to improve the analog and RF figures-of-merit at low current level thanks to minimal impact of series resistance at this current level and reduction of fringing capacitances,<sup>72,73</sup> thanks to longer effective channel length.

Third, as previously mentioned in natural length expression (2) and MASTAR equation, thin BOX further improves the SCE. Employment of thin BOX of 50 nm or below<sup>53,74</sup> allows suppression of fringing electric fields through the BOX thus improving front-gate-to-channel controllability and reducing DIBL. Despite degraded subthreshold slope in long devices with thin BOX due to capacitance increases induced by the use of thin BOX, this degradation becomes smaller in shorter devices<sup>75–77</sup> thanks to better electrostatic coupling and control of SCE. This is translated into thinner depletion thickness in shorter compared to long channel.<sup>78</sup> In addition, thin BOX is also suitable for implementing back-gate biasing schemes used for tuning device characteristics.<sup>79–81</sup> However, the drawback is that it enhances the channel coupling through substrate and if the substrate is depleted, the thin BOX does not gain its advantages. Ground plane implementation with heavily doped substrate<sup>53,82,83</sup> or localized doping,<sup>84–89</sup> have been discussed to reduce the depletion effects in the substrate. The methods in Makiyama et al.<sup>87</sup> and Yan et al.<sup>88,89</sup> claimed through numerical simulation, able to provide better control of short channel effects and thus better DIBL. Eventually, incorporating the GP substrate offers additional attractive package for device scaling solution. It provides as well an easy way to modulate the threshold voltage with Fenouillet-Beranger et al.77,90 and Thomas et al.<sup>86</sup> combining back-gate biasing, constant or connected to drain bias.<sup>84–86</sup> In such ways, multi- $V_{Th}$  option can be achieved based on single metal gate, without complexity in process and channel doping adjustment. With back-gate biasing, the modulation of threshold voltage can even be achieved for device with standard resistivity substrate.<sup>77</sup> Another interesting method to achieve multi-V<sub>Th</sub> option is using gate materials<sup>58,91,92</sup> with different work-functions. In this approach, it requires integration of dual-metal gates scheme and two different ground planes doping (p- or n-GP). Four differences V<sub>Th</sub> can be achieved ranging from 0.32 V up to 0.6 V for both n-MOS and p-MOS devices.91

Finally, exploiting the physical nature of SOI, where the silicon body is located between the gate and buried oxides, basically allows for emulating a double-gate mode (so-called quasi-double gate, QDG, with  $(V_{Sub} - V_{Th2}) = T_{BOX}/T_{gox} \cdot (V_g - V_{Th1})$ . The technique was originally proposed by Balestra et al.<sup>93</sup> in 1987 for 200 nm and 380 nm of silicon body and BOX, respectively. It is more attractive in the

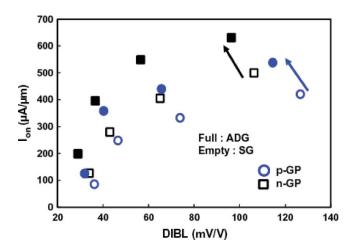

FIG. 6. Improvement in DIBL and Ion in UTBB device operating in asymmetrical double gate.<sup>98</sup>

case of thin body Si where the front and back channels are no longer independent, and as a result of volume inversion concept, controlling the channels from both sides at the same time forces most of the carriers to flow through the middle of the film. The electrons are then localized further away from the oxide interfaces and hence suffer less surface roughness scattering which later significantly increases the carrier mobility compared to single gate device with the same parameters. Significant improvements of subthreshold slope below the theoretical limit of 60 mV/dec have been reported experimentally.<sup>94,95</sup> In addition, it is shown that the transconductance in QDG mode exceeds twice<sup>93,96</sup> or four times<sup>97</sup> the value observed in SG-mode depending on the back-gate biasing even to enhance mobility. However, full QDG mode realizations in such devices may require an over-voltage to be applied to the back gate, which is very complex for CMOS circuits. Thus, in UTBB, as a result of the ultra-thin BOX and the availability of GP, a similar approach can be realized by simply connecting the substrate (or GP contact) to the front gate, i.e.,  $V_{Sub} = V_g$ . Such a connection is known as asymmetric double-gate (ADG) regime<sup>98,99,100</sup> is expected to give a weaker improvement than a pure QDG, but is more practical and easier to employ in circuits. Such operation applied to UTBB devices without a GP was shown to enhance drive current (Ion)<sup>27</sup> and with GP,<sup>98</sup> improve Ion and lower DIBL as well (see Figure 6).

#### 3.3. Figures-of-Merit

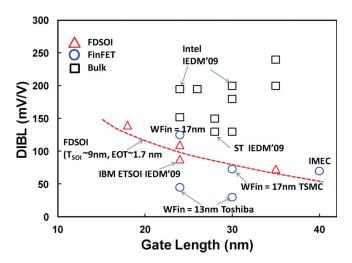

Figure 7 shows the DIBL comparison between bulk, FD-SOI (referring to UTBB) and FinFET devices.<sup>57,58</sup> Due to better electrostatic integrity, FD-SOI devices are known to be suitable to extend the scalability of MOSFETs. Only FinFET with very aggressive scaling fin (13 nm for L = 25 nm) can reduce DIBL further but FinFET poses manufacturing challenges due to 3D-structure devices.

FIG. 7. Summary of DIBL performances between FD-SOI, FinFET, and bulk devices.<sup>57,58</sup>

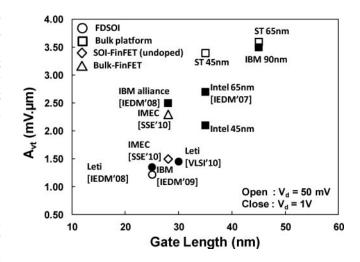

Figure 8 reports the benchmarking of the variability between planar FD-SOI and bulk silicon.<sup>57,58,101,102</sup> Thanks to the use of an undoped channel, which suppresses the random dopant fluctuations, the advantages of FD-SOI are clearly seen with excellent control of threshold voltage variability with lower matching factor ( $A_{vt}$ ) reached for both planar FD-SOI or SOI-FinFETs.

The device scaling for RF is more relaxed, since it is not aggressive as in digital devices. Most available information in literature is dominated by either PD-SOI or bulk Si. Although the scaling is less crucial, nonetheless the benefit of scaling gained in digital can be translated into benefit of RF FoM with condition that the parasitic resistances (gate, source, and drain) and parasitic capacitances are not amplified through fabrication process or architectural technologies. For PD-SOI (mostly reported by IBM), among the highest  $f_T$  and  $f_{max}$  ever reported

FIG. 8. Summary of  $V_{Th}$  matching factor as a function gate length for bulk or FD-SOI devices.<sup>57,58,101–103</sup>

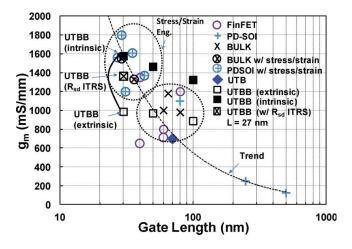

FIG. 9. Benchmarking  $g_{m_{max}}$  with other state-of-the-art technologies as a function of different length.

are 330 and 450 GHz,<sup>104</sup> respectively, for L = 27 nm. The device features Ni silicidation to minimize gate resistances, stress channel engineering for performances enhancement, and optimized layout to minimize the parasitic capacitances. While for bulk Si (mostly reported by Intel), the highest  $f_T$  and  $f_{max}$  are 330 and 420 GHz, respectively, for L = 29 nm.<sup>105</sup> The device employing uni-axial strained silicon, Ni silicide, and excellent control of junction engineering to manage the parasitic resistances. Recently reasonably high f<sub>T</sub> of 300 GHz was reported<sup>63</sup> for FD-SOI (UTB with L = 25 nm,  $T_{Si}$  = 6 nm, and  $T_{BOX} = 145$  nm, by IBM) devices with faceted RSD and undoped channel. As previously mentioned, the faceted RSD does not only reduce the series resistance but also minimizes the parasitic capacitances.  $^{63-65}$  In addition, the faceted RSD increases the strain coupling from stress liners to the channel<sup>66</sup> and hence the silicide contact area.

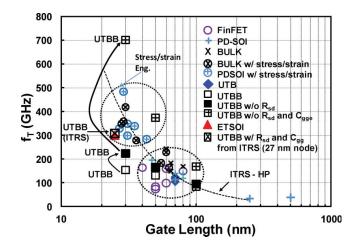

Figure 9 and 10 show the benchmarking of  $g_m$  and  $f_T$  and, respectively, for UTBB<sup>106</sup> with other state-of-the art

FIG. 10. Benchmarking  $f_T$  with other state-of-the-art technologies as a function of different length.

technologies, i.e., PD-SOI, <sup>107–113</sup> FinFET, <sup>114–118</sup> Bulk, <sup>115,117,119–121</sup> UTB, <sup>122,123</sup> stress/strain technologies for PD-SOI  $^{104,124,125}$  or BULK <sup>105,126,127</sup> and FD-SOI (ETSOI<sup>63</sup> and UTBB).

Here, one can see the  $g_{\rm m}$  and  $f_{\rm T}$  of state-of-the art technologies can be grouped differently i.e., with and without strain/stress technologies. The devices with strain/stress technologies result in highest g<sub>m</sub> which translated into highest f<sub>T.</sub> The performance of UTBB device is comparable with FinFET, PD-SOI, UTB and BULK for similar gate length. As the gate length scaled down to 30 nm, extrinsic  $f_T$  as high as ~160 GHz and extrinsic  $g_m$  of  $\sim$ 1000 mS/mm can be achieved. First, the increase of f<sub>T</sub> is attenuated in comparison to expected increase at shorter gate length. This is due to the transistor suffers from the relative increase of the parasitic parameters outside the transistor channel such as the series resistances, overlap and fringing capacitances which do not properly scale down with gate length. In addition to that, for short channel length, the carriers can reach the velocity saturation at high drain voltage and thus g<sub>m</sub> is not longer proportionate to 1/L. Velocity saturation is the phenomena where the carriers reach their peak velocities under the influence of the lateral drain fields. As a result f<sub>T</sub> improvement is less significant in short channel compared to long channel devices. Nevertheless, one still see f<sub>T</sub> is higher in shorter devices compared to long one due to improvement in g<sub>m</sub> and lower parasitic capacitances. Second, the value of extrinsic  $f_T$  is still below ITRS roadmap. Third, f<sub>T</sub> and g<sub>m</sub> have direct correlation, projected in Figures 9 and 10 where higher f<sub>T</sub> is achieved as a result of higher g<sub>m.</sub> (i.e. for stress/strain engineering devices). Finally, ETSOI devices (also with strained silicon engineering) present f<sub>T</sub> almost at the same level compared to other state-of-the-arts strain/stress technologies.

In Md Arshad et al.<sup>98,106</sup>, the estimation of improvement gained in UTBB devices with other state-of-the-art technologies have been made based on intrinsic g<sub>m</sub> and f<sub>T</sub>. One can see that intrinsic g<sub>m</sub> is significantly high, with a value, which is comparable to extrinsic gm obtained from stress/strain engineering devices. However, such improvement is seemed to be not directly translated into intrinsic  $f_T$  (w/o  $R_{sd}$ ) (Figure 10). This gives indication that, the parasitic capacitance is still high in UTBB which affects the intrinsic f<sub>T</sub> (w/o R<sub>sd</sub>). Next, by removing Cgge one can see that the maximum improvement can be obtained in UTBB devices as demonstrated by intrinsic  $f_T$  (w/o  $R_{sd}$  and  $C_{gge}$ ), shown in Figure. 10. This, however, provides an overestimated value of  $f_{T.}$ . Next, they consider  $R_{sd} \sim$ = 300  $\Omega.\mu$ m and C<sub>gg</sub>  $\sim$  = 0.7 fF/ $\mu$ m as in ITRS<sup>2</sup> requirement for FD-SOI technology. The result show that the  $g_m$  (w/  $R_{sd}$ ITRS) and  $f_T$  (w/  $R_{sd}$  and  $C_{gg}$  ITRS) as high as ~1350 mS/mm (Figure 9) and  $\sim$ 310 GHz (Figure 10) can be achieved, respectively. Such values are comparable to strained silicon technology and ETSOI (also with strained silicon technology).

#### 4. CONCLUSION

In this article, we start with comparison between bulk and silicon-on-insulator, then we highlight the main parameter in thin body SOI controlling the short channel effects. After that, we present the digital and RF figures of merit in thin body SOI MOS-FETs. The main advantages of thin body SOI MOSFETs are the back-gate biasing either from the substrate of asymmetrical double gate. These configurations are not achievable in other technologies such as FinFET. Although the thin SOI device is better since its drawbacks are largely overshadowed by its significant advantages, the choice is still surprising since SOI starting material is more expensive than bulk Si as it requires extra processing steps to manufacture. This poses an obstacle to the selection by industry although SOI brings more benefits. However, as the device gate length shrinks down, it is believed the thin body SOI device offers better choice in the future.

#### FUNDING

The authors are grateful to the Department of Higher Education, Ministry of Higher Education, (KPT) for funding this research through the Fundamental Research Grant Scheme (FRGS) with the grant number 9003-00380.

#### REFERENCES

- G. Moore, Cramming more components onto integrated circuits, *Electronics* 38(8),114–117 (1965).

- International Technology Roadmap for Semiconductor (ITRS), 2011 Edition, [Online]. Available: http://www.itrs.net.

- R. Dennard and F. Gaensslen, Design of ion-implanted MOSFET's with very small physical dimensions, *IEEE J. Solid-State Circuits* 9(5), 256–268 (1974).

- G. Baccarani and M. Wordeman, "Generalized Scaling theory and its application to a 1/4 micrometer MOSFET design, *IEEE Trans. Electron Devices* 41(4), 1283–1290 (1984).

- K. J. Kuhn, Moore's law past 32nm: Future challenges in device scaling, in *Inter. Workshop on Computational Electronics* 1–6 (2009).

- M. Bohr, The new era of scaling in an SoC world, in *Solid-State Circuits Conference*, 2009, pp. 23–28.

- M. Bohr, Using innovation to drive Moore's law, in *Interna*tional Conference on Solid-State and Integrated-Circuit Technology 13–15 (2008).

- M. Bohr, The evolution of scaling from the homogeneous era to the heterogeneous era, in *IEEE Electron Devices Meeting* (*IEDM*) 1–6 (2011).

- T. Ghani, M. Armstrong, C. Auth, M. Bost, P. Charvat, G. Glass, T. Hoffmann, K. Johnson, C. Kenyon, J. Klaus, B. McIntyre, K. Mistry, A. Murthy, J. Sandford, M. Silberstein, S. Sivakumar, P. Smith, K. Zawadzki, S. Thompson, and M. Bohr, A 90nm high volume manufacturing logic technology featuring novel 45-nm gate length strained silicon CMOS transistors, in *IEEE Electron Devices Meeting (IEDM)* M, 978–980 (2003).

- 10. R. Gehres, R. Malik, R. Amos, and J. Brown, High volume manufacturing ramp in 90nm dual stress liner technology, in

*IEEE/SEMI Advanced Semiconductor Manufacturing Conference* 411–416 (2006).

- S. E. Thompson, M. Armstrong, C. Auth, M. Alavi, M. Buehler, R. Chau, S. Cea, T. Ghani, G. Glass, T. Hoffman, Chia-Hong Jan, C. Kenyon, J. Klaus, K. Kuhn, Zhiyong Ma, B. Mcintyre, K. Mistry, A. Murphy, B. Obradovic, R. Nagisetty, Phi Nguyen, S. Sivakumar, R. Shaheed, L. Shifren, B. Tufts, S. Tyagi, M. Bohr, Y. El-Mansy, A 90-nm logic technology featuring strained-silicon, *IEEE Trans. Electron Devices* 51(11), 1790– 1797 (2004).

- 12. P. Bai, C. Auth, S. Balakrishnan, M. Bost, R. Brain, V. Chikarmane, R. Heussner, M. Hussein, J. Hwang, D. Ingerly, R. James, J. Jeong, C. Kenyon, E. Lee, S.-H. Lee, N. Lindert, M. Liu, Z. Ma, T. Marieb. A. Murthy, R. Nagisetty, S. Natarajan, J. Neirynck, A. Ott, C. Parker, J Sebastian. R. Shaheed, S. Sivakumar, J. Steigerwald, S. Tyagi, C. Weber, B. Woolery, A. Yeoh, K. Zhang, M. Bohr, 65 nm logic technology featuring 35nm gate lengths, enhanced channel strain, 8 Cu interconnect layers, Low-k ILD and 0.57 μm<sup>2</sup> SRAM cell, in *IEEE Electron Devices Meeting (IEDM)* 657–660 (2004).

- C.-H. Jan, Bai, J. Choi, G. Curello, S. Jacobs, J. Jeong, K. Johnson, D. Jones, S. Klopic, J. Lin, N. Lindert, A. Lio, S. Natarajan, J. Neirynck, P. Packan, J. Park, I. Post, M. Patel, S. Ramey, P. Reese, L. Rockford, A. Roskowski, G. Sacks, B. Turtot, Y. Wang, L. Wei, J. Yip, I. Young, K. Zhang, Y. Zhang, M. Bohr and B. Holt, A 65nm ultra low power logic platform technology using uni-axial strained silicon transistors, in *IEEE Electron Devices Meeting (IEDM)* 8–11 (2005).

- 14. K. Mistry, C. Allen, C. Auth, B. Beattie, D. Bergstrom, M. Bost, M. Brazier, M. Buehler, A. Cappellani, R. Chau, C.-H. Choi, G. Ding, K. Fischer, T. Ghani, R. Grover, W. Han, D. Hanken, M. Hattendorf, J. He, J. Hick, R. Huessner, D. Ingerly, P. Jain, R. James, L. Jong, S. Joshi, C. Kenyon, K. Kuhn, K. Lee, H. Liu, J. Maiz, B. McIntyre, P. Moon, J. Neirynck, S. Pae, C. Parker, D. Parson, C. Prasad, L Pipes, M. Prince, P. Ranader, T. Reynolds, J. Sandford, L. Shifren, J. Sebastian, J. Seiple, D. Simon, D. Sivakumar, P. Smith, C. Thomas, T. Troeger, P. Vandervoorn, S. Williams and K. Zawadzki, A 45nm logic technology with highk+metal gate transistors, strained silicon, 9 Cu interconnect layers, 193nm dry patterning and 100% Pb-free packaging, in *IEEE Electron Devices Meeting (IEDM)* 247–250 (2007).

- 15. C. Auth, A. Cappellani, J.-S. Chun, A. Dalis, A. Davis, T. Ghani, G. Glass, T. Glassman, M. Harper, M. Hattendorf, P. Hentges, S. Jaloviar, S. Joshi, J. Klaus, K. Kuhn, D. Lavric, M. Lu, H. Mariappan, K. Mistry, B. Norris, N. Rahhal-orabi, P. Ranade, J. Sandford, L. Shifren, V. Souw, K. Tone, F. Rambwe, A. Thompson, D. Towner, T. Troeger, P. Vandervoom, C. Wallace, J. Wiedemer and C. Wiegand, 45nm High-k+ metal gate strain-enhanced transistors, in *IEEE Symposium on VLSI Technology (VLSIT)* **12**, 128–129 (2008).

- K. J. Kuhn, Reducing variation in advanced logic technologies: Approaches to process and design for manufacturability of nanoscale CMOS, in *IEEE Electron Devices Meeting (IEDM)* 471–474 (2007).

- P. Packan, S. Akbar, M. Armstrong, D. Bergstrom, M. Brazier, H. Deshpande, K. Dev, G. Ding, T.Ghani, O. Golonzka, W. Han, J. He, R. Heussner, R. James, J. Jopling, C. Kenyon, S.-H. Lee, M. Liu, S. Lodha, B. Mattis, A. Murthy, L. Neiberg, J.

Neirynck, S. Pae, C. Parker, L. Pipes, J. Sebastian, J. Seiple, B. Seiple, B. Sell, A. Sharma, S. Sivakumar, B. Song, A. St. Amour, K. Tone, T. Troeger, C. Weber. K. Zhang, Y. Luo and S. Natarajan, High performance 32nm logic technology featuring 2nd generation high-k + metal gate transistors, in *IEEE Electron Devices Meeting (IEDM)*. 659–662 (2010).

- 18. C.-H. Jan, M. Agostinelli, M. Buehler, Z.-P. Chen, S.-J. Choi, G. Curello, H. Deshpande, S. Gannavaram, W. Hafez, U. Jalan, M. Kang, P. Kolar, K. Komeyli, B. Landau, A. Lake, N. Lazo, S.-H. Lee, T. Leo, J. Lin, N. Lindert, S. Ma, L. McGill, C. Meining, Ap Paliwal, J. Park, K Phoa, I. Post, N. Pradhan, M. Prince, A. Rahman, J. Rizk, L. Rockford, G. Sacks, A. Schmitz, H. Tashiro, C. Tsai, P. Vandervoorn, J. Xu, L. Yang, J.-Y. Yeh, J. Yip, K. Zhang, Y. Zhang and P. Bhai, A 32nm SoC platform technology with 2nd generation high-k/metal gate transistors optimized for ultra low power, high performance, and high density product applications, in *IEEE Electron Devices Meeting (IEDM)* 1–4 (2009).

- M. Bohr and K. Mistry, Intel's revolutionary 22-nm transistor technology. [Online]. Available: http://www.intel.com.

- T. Hiramoto, Transistor evolution for CMOS extension and future information processing technologies, in *Inter. Workshop* on Junction Technology, (IWJT) 3–6 (2009).

- T. Hiramoto, From bulk toward FDSOI and silicon nanowire transistors: Challenges and opportunities, in *Proc. Ultimate Integration on Silicon (ULIS)* c, 1–2 (2011).

- J. P. Colinge, Silicon-on-Insulator Technology: Materials to VLSI, 3rd ed. Kluwer Academic Publishers, Norwell (2004).

- S. Cristoloveanu and G. K. Celler, Chapter 4 SOI materials and devices, in *Handbook of Semiconductor Manufacturing Technology*, CRC Press, Taylor & Francis Group, Boca Raton, Florida (2007).

- S. Cristoloveanu, Silicon on insulator technologies and devices: from present to future, *Solid. State Electron.* 45(8), 1403–1411 (2001).

- Y. Morita, R. Tsuchiya, T. Ishigaki, N. Sugii, T. Iwamatsu, T. Ipposhi, H. Oda, Y. Inoue, K. Torii and S. Kimura, Smallest Vth variability achieved by intrinsic silicon on thin BOX (SOTB) CMOS with single metal gate, in *Symposium on VLSI Technology*, 2008 166–167 (2008).

- S. Makovejev, J.-P. Raskin, M. K. Md Arshad, D. Flandre, S. Olsen, and E. Al, Impact of self-heating and substrate effects on small-signal output conductance in UTBB SOI MOSFETs, *Solid State Electron.* **71**, 93–100 (2012).

- S. Makovejev, V. Kilchytska, M. Md Arshad, D. Flandre, F. Andrieu, O. Faynot, S. Olsen and J.-P. Raskin, Self-heating and substrate effects in ultra-thin body ultra-thin BOX devices, in *Ultimate Integration on Silicon (ULIS)* 130–133 (2011).

- G. K. Celler and S. Cristoloveanu, Frontiers of silicon-on-insulator, J. Appl. Phys. 93(9), 4955 (2003).

- F. Allibert, J. Pretet, G. Pananakakis, and S. Cristoloveanu, Transition from partial to full depletion in silicon-on-insulator transistors: Impact of channel length, *Appl. Phys. Lett.* 84(7), 1192 (2004).

- Soitec Products and Services. [Online]. Available: http://www. soitec.com/pdf/brochure\_products\_services\_en.pdf.

- S. Cristoloveanu, Silicon-on-Insulator Technology, in *The VLSI Handbook*, edited by W. Chen, 3–1 to 3–23. Boca Raton, Taylor

& Francis Group, LLC - CRC Press, Boca Raton, Florida (2007).

- J. P. Colinge, Recent advances and trends in SOI CMOS technology, *Proc. Eur. Solid-State Device Res. Conf.* 2 (1996).

- N. Kistler and J. Woo, Scaling behavior of sub-micron MOS-FETs on fully-depleted SOI, *Solid State Electron.* **39**(4), 445– 454 (1996).

- S. Eminente, S. Cristoloveanu, R. Clerc, A. Ohata, and G. Ghibaudo, Ultra-thin fully-depleted SOI MOSFETs: Special charge properties and coupling effects, *Solid State Electron.* 51(2), 239–244 (2007).

- S. Zaouia, S. Cristoloveanu, M. Sureddin, S. Goktepeli, and A. Perera, Transition from partial to full depletion in advanced SOI MOSFETs: Impact of channel length and temperature, *Solid State Electron.* 51(2), 252–259 (2007).

- R.-H. Yan, A. Ourmazd, and K. F. Lee, Scaling the Si MOS-FET: From bulk to SOI to bulk, *IEEE Trans. Electron Devices* 39(7), 704–710 (1992).

- J.-P. Colinge, Ed., *FinFETs and other multi-gate transistors*, Springer, New York (2008).

- T. Skotnicki. A User's Guide to MASTAR 4, 2000, http://www. itrs.net/Links/2011ITRS/MASTAR2011/MASTARDownload. htm.

- T. Skotnicki, C. Fenouillet-beranger, C. Gallon, S. Monfray, F. Payet, A. Pouydebasque, M. Szczap, A. Farcy, F. Arnaud, S. Clerc, M. Sellier, A. Cathignol, J. Schoellkopf, E. Perea, R. Ferrant, and H. Mingam, Innovative Materials, devices, and CMOS technologies for low-power mobile multimedia, *IEEE Trans. Electron Devices* 55(1), 96–130 (2008).

- T. Skotnicki, Which junction for advanced CMOS? theory, benchmark and predictions, in *Proc. Int. Workshop on Junction Technology* 5–7 (2005).

- T. Skotnicki, Heading for decananometer CMOS-Is navigation among icebergs still a viable strategy?, in *Proc. European Solid-State Device Research Conference* 19–33 (2005).

- T. Skotnicki and F. Boeuf, *High Dielectric Constant Materials:* VLSI MOSFET Applications, Springer Berlin Heidelberg, New York (2004).

- I. De, D. Johri, A. Srivastava, and C. M. Osburn, Impact of gate workfunction on device performance at the 50 nm technology node, *Solid. State. Electron.* 44(6), 1077–1080 (2000).

- 44. M. Bohr, R. Chau, T. Ghani, and K. Mistry, The high-k solution, *IEEE Spectr.* **44**(10), 29–35 (2007).

- M. Jurczak, T. Skotnicki, G. Ricci, Y. Campidelli, C. Hemandez, and D. Bensahel, Study on enhanced performance in NMOSFETs on strained silicon, in *Proc. European Solid-State Device Research Conference* 304–307 (1999).

- M. Frank, High-k/metal gate innovations enabling continued CMOS scaling, in *Proc.of ESSCIRC (ESSCIRC)* i, 25–33 (2011).

- D. Lenoble, Advanced junction fabrication challenges at the 45nm node, 30th Ed. *London*, U.K Semicond. Fabtech Q2, 114–130 (2006).

- H. Iwai, Recent advances and future trends of ULSI technologies, in *Proc. European Solid-State Device Research Conference* 45–51 (1996).

- L. Chang, Y.-K. Choi, D. Ha, P. Ranade, S. Xiong, J. Bokor, C. Hu, and T.-J. King, Extremely scaled silicon nano-CMOS devices," *Proc. IEEE* 91(11), 1860–1873 (2003).

- V. P. Trivedi and J. G. Fossum, Scaling fully depleted SOI CMOS, *IEEE Trans. Electron Devices* 50(10), 2095–2103 (2003).

- T. J. K. Liu and L. Chang, Transistor scaling to the limit, in *Into* the Nano Era, edited by H. R. Huff, pp. 191–223. Berlin Heidelberg, Springer (2009).

- T. Ernst, R. Ritzenthaler, O. Faynot, and S. Cristoloveanu, A model of fringing fields in short-channel planar and triple-gate SOI MOSFETs, *IEEE Trans. Electron Devices* 54(6), 1366– 1375 (2007).

- T. Skotnicki, C. Fenouillet-Beranger, S. Monfray, N. Carriere, and F. Boeuf, Requirements for ultra-thin-film devices and new materials for the CMOS roadmap, *Solid State Electron.* 48(6), 961–967 (2004).

- L. Chang, Y. K. Choi, J. Kedzierski, N. Lindert, P. Xuan, J. Bokor, C. Hu, and T.-J. King, Moore's law lives on, *IEEE Circuits Devices Mag.* 19(1), 35–42 (2003).

- C. Hu, SOI and nanoscale MOSFETs, in *Proc. European Solid-State Device Research Conference* 57(2000), 7–8 (2001).

- Y. Choi, K. Asano, N. Lindert, V. Subramanian, T.-J. King, J. Bokor, and C. Hu, Ultrathin-body SOI MOSFET for deep-subtenth, *IEEE Electron Device Lett.* 21(5), 254–255 (2000).

- O. Faynot, F. Andrieu, C. Fenouillet-Beranger, O. Weber, P. Perreau, L. Tosti, L. Brevard, O. Rozeau, P. Scheiblin, O. Thomas, and T. Poiroux, Planar FDSOI technology for sub 22nm nodes, in *IEEE Symposium on VLSI Technology (VLSIT)* 2010, 26–27 (2010).

- 58. O. Faynot, F. Andrieu, O. Weber, C. Fenouillet-Béranger, P. Perreau, J. Mazurier, T. Benoist, T. Poiroux, M. Vinet, L. Grenouillet, J.-P. Noel, N. Posseme, S. Barnola, F. MArtin, C. Lapeyre, M. Casse, X. Garros, M.-A. Jaud, O. Thomas, G. Cibrario, L. Tosti, L. Brevard, C. Tabone, P. Gaud, S. Barraud, T. Ernst, and S. Deleonibus, Planar fully depleted SOI technology: a powerful architecture for the 20-nm node and beyond, in *IEEE Electron Devices Meeting (IEDM)* 3–2 (2010).

- N. Sugii, R. Tsuchiya, T. Ishigaki, Y. Morita, H. Yoshimoto, T. Kazuyoshi, and S. Kimura, Comprehensive study on Vth variability in silicon on thin BOX (SOTB) CMOS with small random-dopant fluctuation: Finding a way to further reduce variation, in *IEEE Electron Devices Meeting (IEDM)* 1–4 (2008).

- T. Hiramoto, T. Mizutani, and A. Kumar, Suppression of DIBL and current-onset voltage variability in intrinsic channel fully depleted SOI MOSFETs, in *Proc. IEEE International SOI Conference* 9–10 (2010).

- T. Ohtou, N. Sugii, and T. Hiramoto, Impact of parameter variations and random dopant fluctuations on short-channel fully depleted SOI MOSFETs with extremely thin BOX, *IEEE Electron Device Lett.* 28(8), 740–742 (2007).

- F. Andrieu, O. Weber, and S. Baudot, Fully depleted silicon-oninsulator with back bias and strain for low power and high performance applications, in *Inter. Conf. on IC Design and Technology* 59–62 (2010).

- 63. A. Khakifirooz, K. Cheng, and P. Kulkarni, Challenges and opportunities of extremely thin SOI (ETSOI) CMOS

technology for future low power and general purpose systemon-chip applications, in *Proc. VLSI Technology, System and Applications* 110–111 (2010).

- 64. A. Khakifirooz, S. Member, K. Cheng, A. Reznicek, T. Adam, N. Loubet, H. He, J. Kuss, J. Li, P. Kukarani, S. Ponoth, R. Sreenivasan, Q. Liu, B. Doris, and G. Shahidi, Scalability of extremely thin SOI (ETSOI) MOSFETs to sub-20-nm gate length, *IEEE Electron Device Lett.* 33(2), 2011–2013 (2012).

- 65. K. Cheng, A. Khakifirooz, P. Kulkarni, S. Ponoth, J. Kuss, L. F. Edge, A. Kimball, S. Kanakasabapathy, S. Schmitz, A. Reznicek, T. Adam, H. He, S. Mehta, A. Upham, S.-C. Seo, J. L. Herman, R. Johnson, Y. Zhu, P. Jamison, B. S. Haran, Z. Zhu, S. Fan, H. Bu, D. K. Sadana, P. Kozlowski, J. O'Neill, B. Dorins, and G. Shahidi, Extremely thin SOI (ETSOI) technology: Past, present, and future, in *Proc. IEEE International SOI Conference* 1–4 (2010).

- K. Cheng, A. Khakifirooz, and P. Kulkarni, Extremely thin SOI (ETSOI) CMOS with record low variability for low power system-on-chip applications, in *IEEE Electron Devices Meeting* (*IEDM*) 49–52 (2009).

- 67. K. Cheng, A. Khakifirooz, P. Kulkarni, S. Ponoth, B. Haran, A. Kumar, T. Adam, A. Reznicek, N. Loubet, H. He, J. Kuss, M. Wang, T.M. Levin, F. Monsieur, Q. Liu, R. Sreenivasan, J. Cai, A. Kimball, S. Mehta, S. Luning, Y. Zhu, Z. Zhu, T. Yamamoto, A. Bryant, C.-H Lin, S. Naczas, H. Jagannathan, L. F. Edge, S. Allegret-Maret, A. Dube, S. Kanakasabapathy, S Schmitz, A. Inada, S. Seo, M. Raymond, Z. Zhang, A. Yagishita, J. Demarest, J. Li, M. Hopstaken, N. Berliner, A. Upham, R. Johnson, S. Holmes, T. Standaert, M. Smalley, N. Zamdmer, Z. Ren, T. Wu, H. Bu, V. Paruchuri, D. Sadana, V. Narayanan, W. Haensch, J. O-Neill, T. Hook, M. Khare and B. Doris, ETSOI CMOS for system-on-chip applications featuring 22nm gate length, sub-100 nm gate pitch, and 0.08 μm 2 SRAM cell, in *Proc. VLSI Circuits* 8–9 (2011).

- V. Trivedi and J. Fossum, Nanoscale FinFETs with gate-source/ drain underlap, *IEEE Trans. Electron Devices*, **52**(1), 56–62 (2005).

- 69. F. Boeuf, T. Skotnicki, S. Monfray, C. Julien, D. Dutartre, J. Martins, P. Mazoyer, R. Palla, B. Tavel, P. Ribot, E. Sonder-gard and M. Sanquer, 16nm planar NMOSFET manufacturable within state-of-the-art CMOS process thanks to specific design and optimisation, in *IEEE Electron Devices Meeting (IEDM)* 9, 637–640 (2001).

- A. Thean, Z. Shi, and L. Mathew, Performance and variability comparisons between multi-gate FETs and planar SOI transistors, in *IEEE Electron Devices Meeting (IEDM)* 2, 1–4 (2006).

- A. Kranti and G. Alastair Armstrong, Engineering source/drain extension regions in nanoscale double gate (DG) SOI MOS-FETs: Analytical model and design considerations, *Solid State Electron.* 50(3), 437–447 (2006).

- A. Kranti, Rashmi, S. Burignat, J. P. Raskin, and G. Armstrong, Analog/RF performance of sub-100 nm SOI MOSFETs with non-classical gate-source/drain underlap channel design, in *Silicon Monolithic Integrated Circuits in RF Systems (SiRF)* 45–48 (2010).

- A. Kranti, S. Burignat, J. P. Raskin, and G. Armstrong, Underlap channel UTBB MOSFETs for low-power analog/RF applications, in *Proc. International Conference on Ultimate Integration of Silicon (ULIS)* 173–176 (2009).

- C. Fenouillet-Beranger, T. Skotnicki, S. Monfray, N. Carriere, and F. Boeuf, Requirements for ultra-thin-film devices and new materials on CMOS roadmap, in *Proc. International SOI Conference* 00, 145–146 (2003).

- T. Numata and S.-I. Takagi, Device design for subthreshold slope and threshold voltage control in sub-100-nm fully depleted SOI MOSFETs, *IEEE Trans. Electron Devices* 51(12), 2161–2167 (2004).

- T. Numata, K. Uchida, J. Koga, and S. Takagi, Device design for subthreshold slope and threshold voltage control in sub-100-nm fully depleted SOI MOSFETs, in *IEEE International SOI Conference* 51(12), 179–180 (2002).

- 77. C. Fenouillet-Beranger, S. Denorme, P. Perreau, C. Buj, O. Faynot, F. Andrieu, L. Tosti, S. Barnola, T. Salvetat, X. Garros, M. Casse, F. Allain, N. Loubet, L. Pham-Nguyen, E. Deloffre, M. Gros-Jean, R. Beneyton, C. Laviron, M. Marin, C. Leyris, S. Haendler, F. Leverd, P. Gouraud, P. Scheiblin, L. Clement, R. Pantel, S. Deleonibus, and T. Skotnicki, FDSOI devices with thin BOX and ground plane integration for 32nm node and below, *Solid State Electron.* 53(7), 730–734 (2009).

- S. Burignat, D. Flandre, M. K. Md Arshad, V. Kilchytska, F. Andrieu, F. Andrieu, O. Faynot, J.-P Raskin, Substrate impact on threshold voltage and subthreshold slope of sub-32 nm ultra thin SOI MOSFETs with thin buried oxide and undoped channel, *Solid State Electron.* 54(2), 213–219 (2010).

- J. P. Mazellier, F. Andrieu, O. Faynot, L. Brevard, C. Buj, S. Christoloveanu, Y. Le Tiec, and S. Deleonibus, Threshold voltage in ultra thin FDSOI CMOS: Advanced triple interface model and experimental devices, in *Proc. Ultimate Integration on Silicon (ULIS)* 1, 31–34 (2008).

- S. Burignat, D. Flandre, V. Kilchytska, F. Andrieu, O. Faynot, and J.-P. Raskin, Substrate effects in sub-32 nm ultra thin SOI MOSFETs with thin buried oxide, in *Proc. European SOI Conference* 1, 6–7 (2009).

- M. K. Arshad, J. Raskin, S. Member, V. Kilchytska, F. Andrieu, P. Scheiblin, O. Faynot, D. Flandre, and A. D. Results, Extended MASTAR Modeling of DIBL in, *IEEE Trans. Electron Devices* 59(1), 247–251 (2012).

- T. Ernst, C. Tinella, and S. Cristoloveanu, Fringing fields in sub-0.1- μ m fully depleted SOI MOSFETs: optimization of the device architecture, *Solid State Electron*. 46(3), 373–378 (2002).

- S. Monfray, Emerging silicon-on-nothing (SON) devices technology, *Solid State Electron.* 48(6), 887–895 (2004).

- 84. O. Thomas, J. P. Noel, C. Fenouillet-Beranger, M. A. Jaud, J. Dura, P. Perreau, F. Boeuf, F. Andrieu, D. Delprat, F. Boedt, K. Bourdelle, B.-Y. Nguyen, A. Vladimirescu, and A. Amara, 32 nm and beyond Multi-VT Ultra-Thin Body and BOX FDSOI: From device to circuit, in *International Symposium on Circuits and Systems (ISCAS)* 1703–1706 (2010).

- J. Noel, O. Thomas, C. Fenouillet-Beranger, M. Jaud, P. Scheiblin, and A. Amara, A simple and efficient concept for setting up multi-VT devices in thin BOX fully-depleted SOI technology, in *Proc. European Solid-State Device Research Conference* 137–140 (2009).

- C. Fenouillet-Beranger, O. Thomas, P. Perreau, J.-P. Noel, A. Bajolet, S. Haendler, L. Tosti, S. Barnola, R. Beneyton, C. Perrot, C. de Buttet, F. Abbate, F. Baron, B. Pernet, Y. Campidelli,

L. Pinzelli, P. Gouraud, M. Casse, C. Borowiak, O. Weber, F. Andrieu, K.K. Bourdelle, B.-Y. Nguyen, F. Boedt, S. Denorme, F. Boeuf, O. Faynot, T. Skotnicki, Efficient multi-VT FDSOI technology with UTBOX for low power circuit design, in *IEEE Symposium on VLSI Technology (VLSIT)* 65–66 (2010).

- H. Makiyama, Y. Yamamoto, T. Tsunomura, T. Iwamatsu, K. Sonoda, H. Oda, N. Sugii, Y. Yamaguchi, Novel local ground-plane silicon on thin BOX (SOTB) for improving short-channel-effect immunity, in *Proc. European SOI Conference* 2, 27–28 (2012).

- R. Yan, R. Duane, and P. Razavi, LDD and back-gate engineering for fully depleted planar SOI transistors with thin buried oxide, *IEEE Trans. Electron Devices* 57(6), 1319–1326 (2010).

- R. Yan, R. Duane, P. Razavi, A. Afzalian, I. Ferain, C.-W. Lee, N. Dehdashtri, B. Nguten, K.K. Bourdelle, J.P. Colinge, Backgate mirror doping for fully depleted planar SOI transistors with thin buried oxide, in *Proc. VLSI Technology, System and Applications* 76–77 (2010).

- C. Fenouillet-Beranger, P. Perreau, and S. Denorme, Impact of a 10 nm ultra-thin BOX (UTBOX) and ground plane on FDSOI devices for 32 nm node and below, *Solid State Electron.* 54(9), 849–854 (2010).

- 91. O. Weber, F. Andrieu, J. Mazurier, M. Cassé, X. Garros, C. Leroux, P. Perreau, C. Fenouillet-Beranger, S. Barnola, R. Gassilloud, C. Arvet, O. Thomas, J.-P. Noel, O. Rozeau, M.-A. Jaud, T. Poiroux, D. Lafond, A. Toffoli, F. Allain, C. Tabone, L. Tosti, L. Brevard, P. Lehnen, U. Weber, P.K. Baumann, O. Boissiere, W. Schwarzenbach, K. Bourdelle, B.-Y. Nguyen, F. Boeuf, T. Skotnicki and O. Faynot, Work-function engineering in gate first technology for multi-VT dual-gate FDSOI CMOS on UTBOX, in *IEEE Electron Devices Meeting (IEDM)* 3–4 (2010).

- 92. C. Fenouillet-Beranger, P. Perreau, L. Tosti, O. Thomas, J. Noel, T. Benoist, O. Weber, F. Andrieu, A. Bajolet, S. Haendler, M. Casse, X. Garros, K.K. Bourdelle, F. Boedt, O. Faynot and F. Boeuf, Low power UTBOX and back plane (BP) FDSOI technology for 32 nm node and below, in *IEEE International Conference on IC Design & Technology (ICICDT)* 1–4 (2011).

- F. Balestra and S. Cristoloveanu, Double-gate silicon-on-insulator transistor with volume inversion: A new device with greatly enhanced performance, *IEEE Electron Device Lett.* L(9), 410– 412 (1987).

- V. Kilchytska, T. Chung, H. van Meer, K. De Meyer, J. Raskin, and D. Flandre, Investigation of charge control-related performances in double-gate SOI MOSFETs, in *Proc. Int. SOI Symp.* (ECS), Paris c, 225–230 (2003).

- A. Ohata, J. Pretet, S. Cristoloveanu, and A. Zaslavsky, Correct biasing rules for virtual DG mode operation in SOI-MOSFETs, *IEEE Trans. Electron Devices* 2(1), 124–125 (2005).

- F. Allibert, From SOI materials to innovative devices, *Solid State Electron*. 45(4), 559–566 (2001).

- T. Ernst, S. Cristoloveanu, G. Ghibaudo, T. Ouisse, S. Horiguchi, Y. Ono, Y. Takahashi and K. Murase, Ultimately thin double-gate SOI MOSFETs," *IEEE Trans. Electron Devices* 50(3), 830–838 (2003).

- M. K. Md Arshad, S. Makovejev, S. Olsen, F. Andrieu, J.-P. Raskin, D. Flandre, and V. Kilchytska, UTBB SOI MOSFETs analog figures of merit : Effects of ground plane and asymmetric double-gate regime, *Solid State Electron*. 90, 56–64 (2013).

- M. Md Arshad and U. Hashim, Emulation of Double Gate Transistor in Ultra- Thin Body with Thin Buried Oxide SOI MOS-FETs, in *IEEE Reg. Symposium on Microelectronics* 162–165 (2013).

- 100. N. Othman, M.K. Md Arshad, U. Hashim, S.N.Syed Sabki. Impact of different ground planes of UTBB SOI MOSFETs under the single-gate (SG) and double-gate (DG) operation mode. IEEE International Conference on Semiconductor Electronics (ICSE 2014). 27–29 August 2014: pp. 88–91.

- O. Weber, O. Faynot, and F. Andrieu, High immunity to threshold voltage variability in undoped ultra-thin FDSOI MOSFETs and its physical understanding, in *IEEE Electron Devices Meeting (IEDM)* 10–13 (2008).

- L. Clavelier, C. Deguet, and L. Di Cioccio, Engineered substrates for future More Moore and More than Moore integrated devices, in *IEEE Electron Devices Meeting (IEDM)* 42–45 (2010).

- B.-Y. Nguyen and C. Mazuré, The era of fully-depleted devices, Mag. Solid State Technol. 54(10) (2011).

- S. Lee, L. Wagner, and B. Jagannathan, Record RF performance of sub-46 nm L/sub gate/NFETs in microprocessor SOI CMOS technologies, in *IEEE Electron Devices Meeting* (*IEDM*) 241–244 (2005).

- 105. I. Post, M. Akbar, and G. Curello, A 65 nm CMOS SOC technology featuring strained silicon transistors for RF applications, in *IEEE Electron Devices Meeting (IEDM)* 245, 8–10 (2006).

- 106. M. K. MdArshad, V. Kilchytska, M. Emam, F. Andrieu, D. Flandre, and J.-P. Raskin, Effect of parasitic elements on UTBB FD SOI MOSFETs RF figures of merit, *Solid State Electron.* 97, 38–44 (2014).

- 107. V. Kilchytska, A. Neve, L. Vancaillie, D. Levacq, S. Adriaensen, K. De Meyer, C. Raynaud, M. Dehan, J.-P. Raskin, and D. Flandre, Influence of device engineering on the analog and RF performances of SOI MOSFETs, *IEEE Trans. Electron Devices* 50(3), 577–588 (2003).

- S. Narasimha, A. Ajmera, and H. Park, High performance sub-40 nm CMOS devices on SOI for the 70 nm technology node, in *IEEE Electron Devices Meeting (IEDM)* 625–628 (2001).

- 109. T. Matsumoto, S. Maeda, and K. Ota, 70 nm SOI-CMOS of 135 GHz fmax with dual offset-implanted source-drain extension structure for RF/analog and logic applications, in *IEEE Electron Devices Meeting (IEDM)* 219–222 (2001).

- 110. Y. Momiyama, T. Hirose, and H. Kurata, A 140 GHz ft and 60 GHz fmax DTMOS integrated with high-performance SOI logic technology, in *IEEE Electron Devices Meeting (IEDM)* 451–454 (2000).

- N. Zamdmer, J. Plouchart, and J. Kim, Suitability of scaled SOI CMOS for high-frequency analog circuits, in *Proc. European Solid-State Device Research Conference* 511–514 (2002).

- 112. T. Hirose, Y. Momiyama, and M. Kosugi, A 185 GHz fmax SOI DTMOS with a new metallic overlay-gate for low-power RF applications, in *IEEE Electron Devices Meeting (IEDM)* 943–945 (2001).

- 113. N. Zamdmer, A. Kay, J. Plouchart, L. Wagner, N. Fong, K. A. Jenkin, W. Jin, P. Smeys, I. Yang, G. Shahidi, and F. Assader-ghi, A 0.13-μm SOI CMOS technology for low-power digital and RF applications, in *IEEE Symposium on VLSI Technology* (VLSIT) 671(1999), 85–86 (2001).

- 114. D. Lederer, V. Kilchytska, T. Rudenko, N. Collaert, D. Flandre, A. Dixit, K. De Meyer, J.-P. Raskin, FinFET analogue characterization from DC to 110 GHz, *Solid State Electron.* **49**(9), 1488–1496 (2005).

- B. Parvais, A. Mercha, and N. Collaert, The device architecture dilemma for cmos technologies: opportunities & challenges of FinFET over planar MOSFET, in *IEEE Symposium on VLSI Technology (VLSIT)* 80–81 (2009).

- 116. D. Lederer, B. Parvais, A. Mercha, N. Collaert, M. Jurczak, J.-P. Raskin, and S. Decoutere, Dependence of FinFET RF performance on fin width, in *Proc. Silicon Monolitic Integrated Circuits in RF Systems (SiRF)* 8–11 (2006).

- 117. V. Subramanian, B. Parvais, J. Borremans, A. Mercha, D. Linten, P. Wambacq, J. Loo, M. Dehan, C. Gustin, N. Collaert, S. Kubicek, R. Lander, J. Hooker, F. Cubaynes, S. Donnay, M. Jurczak, G. Groeseneken, W. Sansen, and S. Decoutere, Planar bulk MOSFETs versus FinFETs: an analog/RF perspective, *IEEE Trans. Electron Devices* 53(12), 3071–3079 (2006).

- W. Jeamsaksiri, M. Jurczak, and L. Grau, Gate-source-drain architecture impact on DC and RF performance of sub-100-nm elevated source/drain NMOS transistors, *IEEE Trans. Electron Devices* 50(3), 610–617 (2003).

- H. Momose, E. Morifuji, and T. Yoshitomi, Cutoff frequency and propagation delay time of 1.5-nm gate oxide CMOS, *IEEE Trans. Electron Devices* 48(6), 1165–1174 (2001).

- L. Tiemeijer, R. Havens, and R. De Kort, Record RF performance of standard 90 nm CMOS technology, in *IEEE Electron Devices Meeting (IEDM)* 441–444 (2004).

- 121. C. Chen, C. Chang, and C. Chao, A 90 nm CMOS MS/RF based foundry SOC technology comprising superb 185 GHz fT RFMOS and versatile, high-Q passive components for cost/performance optimization, in *IEEE Electron Devices Meeting* (*IEDM*) 39–42 (2003).

- 122. T. C. Lim, E. Bernard, O. Rozeau, T. Ernst, B. Guillaumot, N. Vulliet, C. Buj-Dufournet, M. Paccaud, S. Lepilliet, G. Dambrine, and F. Danneville, Analog/RF performance of multichannel SOI MOSFET, *IEEE Trans. Electron Devices* 56(7), 1473–1482 (2009).

- 123. T. Lim, O. Rozeau, C. Buj, M. Paccaud, G. Dambrine, and F. Danneville, HF characterisation of sub-100nm UTB-FDSOI with TiN/HfO2 gate stack, in *Proc. Ultimate Integration on Silicon (ULIS)* 145–148 (2008).

- 124. S. Lee, B. Jagannathan, and S. Narasimha, Record RF performance of 45-nm SOI CMOS technology, in *IEEE Electron Devices Meeting (IEDM)* 255–258 (2007).

- 125. S. Lee, J. Kim, D. Kim, B. Jagannathan, C. Cho, J. Johnson, B. Dufrene, N. Zamdmer, L. Wagner, R. Williams, D. Friend, K. Rim, J. Pekarik, S. Springer, J.-O. Plouchart, and G. Freeman, SOI CMOS technology with 360 GHz fT NFET, 260 GHz fT PFET, and record circuit performance for millimeter-wave digital and analog system-on-chip applications, in 2007 IEEE Symposium on VLSI Technology 54–55 (2007).

- 126. H. Li, B. Jagannathan, J. Wang, T.-C. Su, S. Sweeney, J. J. Pekarik, Y. Shi, D. R. Greenberg, Z. Jin, R. A. Groves, L. Wagner, and S. Csutak, Technology scaling and device design for 350 GHz RF performance in a 45 nm bulk CMOS process, in *IEEE Symposium on VLSI Technology* (*VLSIT*) 1–2 (2007).